A device driver accesses a parallel or serial port, keyboard, mice, disk, network, display, file, pipe and socket at specific addresses. An OS also provides device driver codes for system-port addresses and for hardware access mechanisms.

A device manager software provide codes for detecting the presence of devices, for initializing these and for testing the devices that are present. The manager includes software for allocating and registering port (in fact, it may be a register or memory) addresses for the various devices at distinctly different addresses, including codes for detecting any collision between these, if any. It ensures that any device accesses to one task only at any given instant. It takes into account that virtual devices may also have addresses that are allocated by the manager.

An OS also provides and executes modules for managing devices that associate with an embedded system. The underlying principle is that at an instant, only one physical or virtual device should get access to or from one task only.

Sections 4.2.4 and 8.6.1 will describe device drivers and device management in detail. The OS also provides and manages virtual devices such as pipes and sockets. Sections 7.14 and 7.15 describe these in detail.

For designing embedded-software, two types of devices are considered: physical and virtual. Physical devices include keypad, printer or display unit. A virtual device could be a file or pipe or socket or RAM disks. Device drivers and device manager software are needed in the system. The RTOS includes device-drivers and a device manager to control and facilitates the use of the number of physical and virtual devices in the system.

# 1.4.8 Software Tools for Designing an Embedded System

Table 1.2 lists the applications of software tools for assembly language programming, high level language programming, RTOS, debugging and system integration.

Table 1.2 Software modules and tools for designing of an embedded system

| Software Tools | Application                                                                                                                                                                                                                                                                                                                                                                  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Editor         | For writing C codes or assembly mnemonics using the keyboard of the PC for entering the program. Allows the entry, addition, deletion, insert, appending previously written lines or files, merging record and files at the specific positions. Creates a source file that stores the edited file. It also has an appropriate name [provided by the programmer].             |  |

| Interpreter    | For expression-by-expression (line-by-line) translation to machine-executable codes.                                                                                                                                                                                                                                                                                         |  |

| Compiler       | Uses the complete set of codes. It may also include codes, functions and expressions fre the library routines. It creates a file called object file.                                                                                                                                                                                                                         |  |

| Assembler      | For translating assembly mnemonics into binary opcodes (instructions), that is, into an executable file called binary file and for making a list file that can be printed. The list file has address, source code (assembly language mnemonics) and hexadecimal object codes. The file has addresses that reallocate during the actual run of the assembly language program. |  |

(Contd)

| Software Tools                     | Application                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Cross assembler                    | For converting object codes or executable codes for a processor to other codes for anot processor and vice versa. The cross-assembler assembles the assembly codes of the processor as the assembly codes of the processor of the PC used in system developmed Later, it provides the object codes for the target processor. These codes will be the of actually needed in the final developed system. |  |  |

| Simulator                          | To simulate all functions of an embedded system circuit including that or additional mem and peripherals. It is independent of a particular target system. It also simulates the process that will execute when the codes of a particular processor execute.                                                                                                                                           |  |  |

| Source-code engineering software   | For source code comprehension, navigation and browsing, editing, debugging, configur (disabling and enabling the C++ features) and compiling.                                                                                                                                                                                                                                                          |  |  |

| RTOS                               | Refer Chapters 8 to 10.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Stethoscope                        | For dynamically tracking the changes in any program variable or parameter. It demonstrates the sequence of multiple processes (tasks, threads, service routines) that execute and alrecords the entire time history.                                                                                                                                                                                   |  |  |

| Trace scope                        | To help in tracing the changes in modules and tasks with time on the X-axis. A state actions also produces the desired time scales and the time expected to be taken for differ tasks.                                                                                                                                                                                                                 |  |  |

| Integrated development environment | This is a development software and hardware environment that consists of simulators we editors, compilers, assemblers, RTOS, debuggers, stethoscope, tracer, emulators, analyzers, and application code burners in PROM or flash.                                                                                                                                                                      |  |  |

| Prototyper                         | This simulates and does source code engineering including compiling, debugging an browsing and summarizing the complete status of the final target system during the development phase.                                                                                                                                                                                                                |  |  |

| Locator#                           | This uses a cross-assembler output and a memory allocation map and provides the local program output as a hex-file. It is the final step of the software design procession embedded system.                                                                                                                                                                                                            |  |  |

<sup>#</sup> The locator program output is in the Intel hex file or Motorola S-record format.

Software tools are used to develop software for designing an embedded system. Debugging tools, such as a stethoscope, trace scope, and sophisticated tools such as an integrated development environment and prototype development tools, are needed for the integrated development of system software and hardware.

# 1.4.9 Software Tools Required in Exemplary Cases

Table 1.3 gives the various tools needed to design exemplary systems.

RTOS is essential in most embedded systems to process multiple tasks and ISRs. Embedded systems for medium scale and sophisticated applications need a number of sophisticated software and debugging tools.

Table 1.3 Software tools required in exemplary systems

| Software<br>Tools                  | Automatic<br>Chocolate<br>Vending<br>Machine <sup>&amp;</sup> | Data<br>Acquisition<br>System | Robot | Mobile<br>Phone | Adaptive<br>Cruise Control<br>System with<br>String Stability# | Voice<br>Processor |

|------------------------------------|---------------------------------------------------------------|-------------------------------|-------|-----------------|----------------------------------------------------------------|--------------------|

| Editor                             | Yes                                                           | Yes                           | Yes   | Yes             | Yes                                                            | NR                 |

| Interpreter                        | Yes                                                           | NR                            | Yes   | NR              | NR                                                             | NR                 |

| Co <b>m</b> piler                  | Yes                                                           | Yes                           | Yes   | Yes             | Yes                                                            | Yes                |

| As <b>se</b> mbler                 | Yes                                                           | Yes                           | Yes   | No              | No                                                             | No                 |

| Cross Assembler                    | NR                                                            | Yes                           | Yes   | No              | No                                                             | No                 |

| Locator                            | Yes                                                           | Yes                           | Yes   | Yes             | Yes                                                            | Yes                |

| Simulator                          | NR                                                            | Yes                           | Yes   | Yes             | Yes                                                            | Yes                |

| Source code engineering software   | NR                                                            | NR                            | NR    | Yes             | Yes                                                            | Yes                |

| RTOS                               | Yes                                                           | MR                            | Yes   | Yes             | Yes                                                            | Yes                |

| Stethoscope                        | NR                                                            | NR                            | NR    | Yes             | Yes                                                            | Yes                |

| Trace scope                        | NR                                                            | NR                            | NR    | Yes             | Yes                                                            | Yes                |

| Integrated development environment | NR                                                            | Yes                           | Yes   | Yes             | Yes                                                            | Yes                |

| Prototyper                         | NR                                                            | No                            | No    | Yes             | Yes                                                            | Yes                |

Note: NR means not required. MR means may be required in a specific complex system but not compulsorily needed.

# **EXAMPLES OF EMBEDDED SYSTEMS**

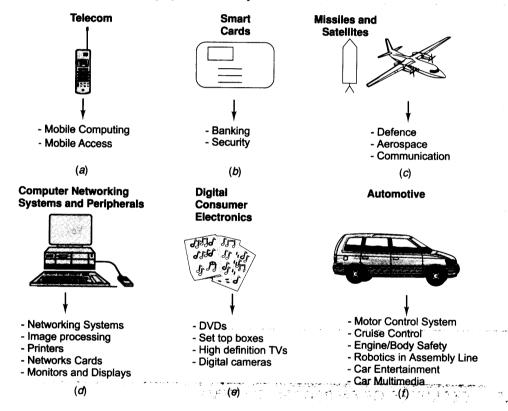

Embedded systems have very diversified applications. A few select application areas of embedded systems are telecommunications, smart cards, missiles and satellites, computer networking, digital consumer electronics, and automotives. Figure 1.9 shows the applications of embedded systems in these areas.

A few examples of small scale embedded system applications are as follows:

- 1. Point of sales terminals: automatic chocolate vending machine

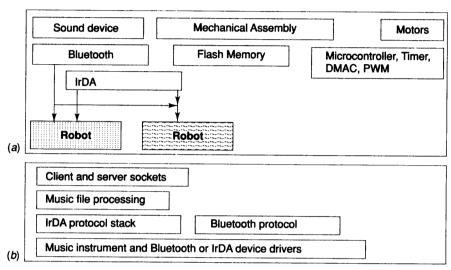

- 2. Stepper motor controllers for a robotics system

- 3. Washing or cooking systems

- 4. Multitasking toys

- 5. Microcontroller-based single or multidisplay digital panel meter for voltage, current, resistance and frequency

- 6. Keyboard controller

- 7. SD, MMI and network access cards

- 8. CD drive or hard disk drive controller

- 9. The peripheral controllers of a computer, for example, a CRT display controller, a keyboard controller, a DRAM controller, a DMA controller, a printer controller, a laser printer controller, a LAN controller, a disk drive controller

- 10. Fax or photocopy or printer or scanner machine

- 11. Remote (controller) of TV

- 12. Telephone with memory, display and other sophisticated features

Fig. 1.9 Applications of the embedded systems in various areas

- 13. Motor controls systems—for example, an accurate control of speed and position of the d.c. motor, robot and CNC machine; automotive applications such as closed loop engine control, dynamic ride control, and an antilock braking system monitor

- 14. Electronic data acquisition and supervisory control system

- 15. Electronic instruments, such as an industrial process controller

- 16. Electronic smart weight display system and an industrial moisture recorder cum controller

- 17. Digital storage system for a signal wave form or for electric or water meter reading system

- 18. Spectrum analyzer

- 19. Biomedical systems such as an ECG LCD display cum recorder, a blood-cell recorder cum analyzer, and a patient monitor system

Some examples of medium scale embedded systems are as follows:

- 20. Computer networking systems, for example, a router, a front-end processor in a server, a switch, a bridge, a hub and a gateway

- 21. For Internet appliances, there are numerous application systems (i) An intelligent operation, administration and maintenance router (IOAMR) in a distributed network and (ii) Mail client card to store e-mail and personal addresses and to smartly connect to a modem or server

- 22. Entertainment systems such as a video game and a music system

- 23. Banking systems, for example, bank ATM and credit card transactions

- 24. Signal tracking systems, for example, an automatic signal tracker and a target tracker

- 25. Communication systems such as a mobile communication SIM card, a numeric pager, a cellular phone, a cable TV terminal and a FAX transceiver with or without a graphic accelerator

- 26. Image filtering, image processing, pattern recognizer, speech processing and video processing

- 27. Video games

- 28. A system that connects a pocket PC to the automobile driver mobile phone and a wireless receiver. The system then connects to a remote server for Internet or e-mail or to a remote computer at an ASP (application service provider)

- 29. A personal information manager using frame buffers in handheld devices

- 30. Thin client [A thin client provides disk-less nodes with remote boot capability]. Application of thinclient accesses to a data centre from a number of nodes; in an Internet laboratory accesses to the Internet leased line through a remote server.

- 31. Embedded firewall / router using ARM7/ multiprocessor with two Ethernet interfaces and interfaces support to PPP, TCP/IP and UDP protocols.

Examples of sophisticated embedded systems are as follows:

- 32. Mobile smart phones and computing systems

- 33. Mobile computer

- 34. Embedded systems for wireless LAN and for convergent technology devices

- 35. Embedded systems for video, interactive video, broadband IPv6 (Internet Protocol version 6) Internet and other products, real time video and speech or multimedia processing systems

- 36. Embedded interface and networking systems using high speed (400 MHz plus), ultra high speed (10 Gbps) and a large bandwidth: Routers, LANs, switches and gateways, SANs (Storage Area Networks), WANs (Wide Area Networks)

- 37. Security products and high-speed Network security. Gigabit rate encryption rate products

# 16

# EMBEDDED SYSTEM-ON-CHIP (SoC) AND USE OF VLSI CIRCUIT DESIGN TECHNOLOGY

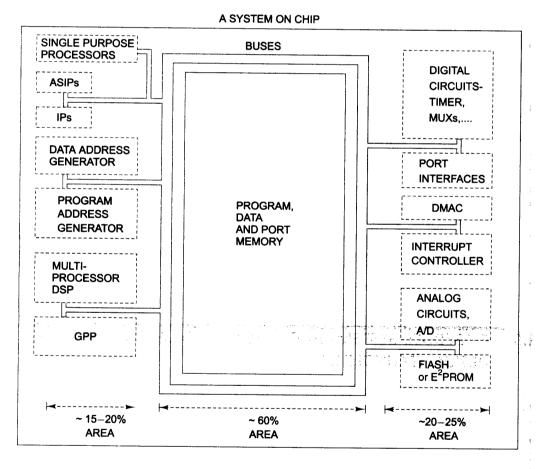

Lately, embedded systems are being designed on a single silicon chip, called *System on chip (SoC)*, a design innovation. SoC is a system on a VLSI chip that has all the necessary analog as well as digital circuits, processors and software.

A SoC may be embedded with the following components:

- 1. Embedded processor GPP or ASIP core,

- 2. Single purpose processing cores or multiple processors,

- 3. A network bus protocol core,

- 4. An encryption function unit,

- 5. Discrete cosine transforms for signal processing applications,

- 6. Memories,

- 7. Multiple standard source solutions, called IP (Intellectual Property) cores,

- 8. Programmable logic device and FPGA (Field Programmable Gate Array) cores,

- 9. Other logic and analog units.

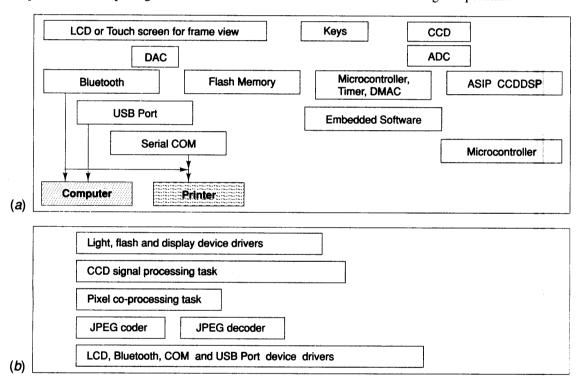

An exemplary application of such an embedded SoC is the mobile phone. Single purpose processors, ASIPs and IPs on an SoC are configured to process encoding and deciphering, dialing, modulating, demodulating, interfacing the key pad and multiple line LCD matrix displays or touch screen, storing data input and recalling data from memory. Figure 1.10 shows an SoC that integrates internal ASICs, internal processors (ASIPs), shared memories and peripheral interfaces on a common bus. Besides a processor, memories and digital circuits with embedded software for specific applications, the SoC may possess analog circuits as well.

Fig. 1.10 A SoC embedded system and its common bus with internal ASIPs, internal processors, IPs, shared memories and peripheral interfaces

### 1.6.1 Application Specific IC (ASIC)

ASICs are designed using the VLSI design tools with the processor GPP or ASIP and analog circuits embedded into the design. The designing is done using the Electronic Design Automation (EDA) tool. [For design of an ASIC, a High-level Design Language (HDL) is used].

#### 1.6.2 IP Core

On a VLSI chip, there may be integration of high-level components. These components possess gate-level sophistication in circuits above that of the counter, register, multiplier, floating point operation unit and ALU. A standard source solution for synthesizing a higher-level component by configuring an FPGA core or a core of VLSI circuit may be available as an Intellectual Property, called (IP). The designer or the designing company holds the copyright for the synthesized design of a higher-level component for gate-level implementation of an IP. One might have to pay royalty for every chip shipped. An embedded system may incorporate several IPs.

- An IP may provide hardwired implementable design of a transform, an encryption algorithm or a deciphering algorithm.

- An IP may provide a design for adaptive filtering of a signal.

- An IP may provide a design for implementing Hyper Text Transfer Protocol (HTTP) or File Transfer Protocol (FTP) or Bluetooth protocol to transmit a web page or a file on the Internet.

- An IP may be designed for a USB or PCI bus controller. [Sections 3.10.3 and 3.12.2]

# 1.6.3 FPGA Core with Single or Multiple Processors

Suppose an embedded system is designed with a view to enhancing functionalities in future. An FPGA core is then used in the circuits. It consists of a large number of programmable gates on a VLSI chip. There is a set of gates in each FPGA cell, called macro cell. Each cell has several inputs and outputs. All cells interconnect like an array (matrix). Each interconnection is programmable through the associated RAM in an FPGA programming tool. An FPGA core can be used with a single or multiple processor.

Consider the algorithms for the following: Fourier transform (FT) and its inverse (IFT), DFT or Laplace transform and its inverse, compression or decompression, encrypting or deciphering, specific pattern recognition (for recognizing a signature or finger print or DNA sequence). We can configure an algorithm into the logic gates of FPGA. It gives hardwired implementation for a processing unit. It is specific to the needs of the embedded system. An algorithm of the embedded software can implement in one of the FPGA sections and another algorithm in its other section.

FPGA cores with a single or multiple processor units on chip are used. One example of such core is Xilinx Virtex-II Pro FPGA XC2VP125. XC2VP125 from Xilinx has 125136 logic cells in the FPGA core with four IBM PowerPCs. It has been used as a data security solution with encryption engine and data rate of 1.5 Gbps. Other examples of embedded systems integrated with logic FPGA arrays are DSP-enabled, real-time video processing systems and line echo eliminators for the Public Switched Telecommunication Networks (PSTN) and packet switched networks. [A packet is a unit of a message or a flowing data such that it can follow a programmable route among the number of optional open routes available at an instance.]

# 1.7 COMPLEX SYSTEMS DESIGN AND PROCESSORS

# 1.7.1 Embedding a Microprocessor

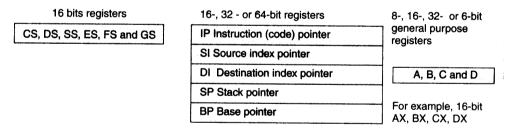

A General Purpose Processor microprocessor can be embedded on a VSLI chip. Table 1.4 lists different streams of microprocessors embedded in a complex system design.

Table 1.4 Important microprocessors used in embedded systems

| Stream   | Microprocessor Family | Source   | CISC or RISC or Both features |  |

|----------|-----------------------|----------|-------------------------------|--|

| Stream 1 | 68HCxxx               | Motorola | CISC                          |  |

| Stream 2 | 80x86                 | Intel    | CISC                          |  |

| Stream 3 | SPARC                 | Sun      | RISC                          |  |

| Stream 4 | ARM                   | ARM      | RISC with CISC functionality  |  |

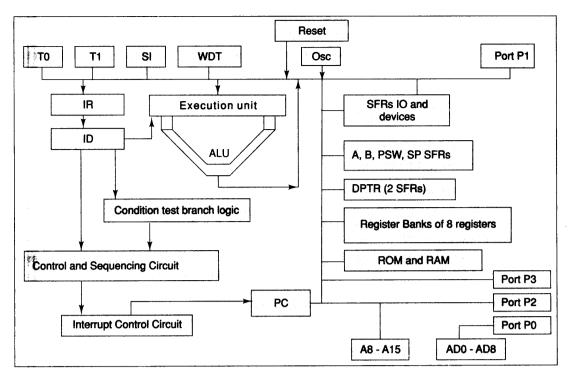

#### 1.7.2 Embedding a Microcontroller

Microcontroller VLSI cores or chips for embedded systems are usually among the five streams of families given in Table 1.5.

Table 1.5 Major microcontrollers<sup>®</sup> used in the embedded systems

| Stream    | Microcontroller Family                                                                                  | Source                                                          | CISC or RISC or Both                 |

|-----------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------|

| Stream 1  | 68HC11xx, HC12xx, HC16xx                                                                                | Motorola                                                        | CISC                                 |

| Stream 2  | 8051, 8051MX                                                                                            | Intel, Philips                                                  | CISC                                 |

| Stream 3  | PIC 16F84 or 16C76, 16F876 and PIC18                                                                    | Microchip                                                       | CISC                                 |

| Stream 4* | Microcontroller Enhancements of CORTEX-M3<br>ARM9/ARM7 from Philips, Samsung and<br>ST Microelectronics | ARM, Texas, Philips,<br>Samsung and ST<br>Microelectronics etc. | RISC Core with<br>CISC functionality |

<sup>&</sup>lt;sup>®</sup> Other popular microcontrollers are as follows. (i) Hitachi H8x family and SuperH 7xxx. (ii) Mitsubishi 740, 7700, M16C and M32C families. (iii) National Semiconductor COP8 and CR16 /16C. (iv) Toshiba TLCS 900S (v) Texas Instruments MSP 430 for low voltage battery based system. (vi) Samsung SAM8. (vii) Ziglog Z80 and eZ80

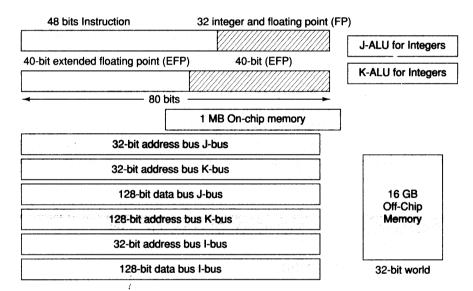

### 1.7.3 Embedding a DSP

A digital signal processor (DSP) is a processor core or chip for the applications that process digital signals. [For example, filtering, noise cancellation, echo elimination, compression and encryption applications.] Just as a microprocessor is the most essential unit of a computing system, a DSP is essential unit of an embedded

system in a large number of applications needing processing of signals. Exemplary applications are in image processing, multimedia, audio, video, HDTV, DSP modem and telecommunication processing systems. DSPs also find use in systems for recognizing image pattern or DNA sequence.

DSP as an ASIP is a single chip or core in a VLSI unit. It includes the computational capabilities of a microprocessor and Multiply and Accumulate (MAC) units. A typical MAC has a  $16 \times 32$  MAC unit.

DSP executes discrete-time, signal-processing instructions. It has Very Large Instruction Word (VLIW) processing capabilities; it processes Single Instruction Multiple Data (SIMD) instructions; it processes Discrete Cosine Transformations (DCT) and inverse DCT (IDCT) functions. The latter are used in algorithms for signal analyzing, coding, filtering, noise cancellation, echo elimination, compressing and decompressing, etc.

Major DSPs for embedded systems are from the three streams given in Table 1.6.

Table 1.6 Important digital signal processor<sup>@</sup> used in the embedded systems

| Stream   | DSP Family                   | Source        |

|----------|------------------------------|---------------|

| Stream 1 | TMS320Cxx, OMAP <sup>1</sup> | Texas         |

| Stream 2 | Tiger SHARC                  | Analog Device |

| Stream 3 | 5600xx                       | Motorola      |

| Stream 4 | PNX 1300, 1500 <sup>2</sup>  | Philips       |

<sup>&</sup>lt;sup>1</sup>For example, TMS320C62XX a fixed point 200 MHz DSP (Section 2.3.5).

#### 1.7.4 Embedding an RISC

A RISC microprocessor provides the speedy processing of instructions, each in a single clock-cycle. This facilitates pipelining and superscalar processing. Besides greatly enhanced capabilities mentioned above, there is great enhancement of speed by which an instruction from a set is processed. Thumb<sup>®</sup> instruction set is a new industry standard that also gives a reduced code density in ARM RISC processor. RISCs are used when the system needs to perform intensive computation, for example, in a speech processing system.

# 1.7.5 Embedding an ASIP

ASIP is a processor with an instruction set designed for specific application areas on a VLSI chip or core. ASIP examples are microcontroller, DSP, IO, media, network or other domain-specific processor.

Using VLSI design tools, an ASIP with instructions sets required in the specific application areas can be designed. The ASIP is programmed using the instructions of the following functions: DSP, control signals processing, discrete cosine transformations, adaptive filtering and communication protocol-implementing functions.

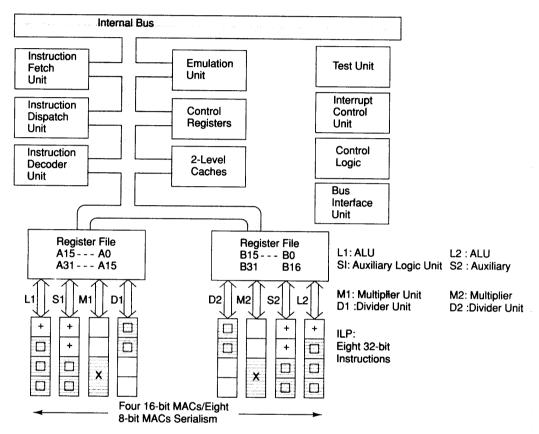

# 1.7.6 Embedding a Multiprocessor or Dual Core Using GPPs

In an embedded system, several processors or dual core processors may be needed to execute an algorithm fast within a strict deadline. For example, in real-time video processing, the number of MAC operations needed per second may be more than is possible from one DSP unit. An embedded system then incorporates two or more processors running in synchronization. An example of using multiple ASIPs is high-definition television signals processing. [High definition means that the signals are processed for a noise-free, echo-cancelled transmission, and for obtaining a flat high-resolution image (1920  $\times$  1020 pixels) on the television screen.] A cell phone or digital camera is another application with multiple ASIPs.

<sup>&</sup>lt;sup>2</sup>Media processor, which besides multimedia DSP operations, also does network stream data packet processing.

In a cell phone, a number of tasks have to be performed: (a) Speech signal-compression and coding. (b) Dialing (c) Modulating and Transmitting (d) Demodulating and Receiving (e) Signal decoding and decompression (f) Keypad interface and display interface handling (g) Short Message Service (SMS) protocolbased messaging (h) SMS message display. For all these tasks, a single processor does not suffice. Suitably synchronized multiple processors are used.

Consider a video conferencing system. In this system, a quarter common intermediate format—Quarter-CIF—is used. The number of image pixels is just  $144 \times 176$  as against  $525 \times 625$  pixels in a video picture on TV. Even then, samples of the image have to be taken at a rate of  $144 \times 176 \times 30 = 760320$  pixels per second and have to be processed by compression before transmission on a telecommunication or Virtual Private Network (VPN). [Note: The number of frames are 25 or 30 per second (as per the standard adopted) for real-time displays and in motion pictures.] A single DSP-based embedded system does not suffice to get real-time images during video conferencing. Real-time video processing and multimedia applications most often need a multiprocessor unit in the embedded system.

Multiple processors or dual core processors are used when a single microprocessor does not meet the needs of the different tasks that execute concurrently. The operations of all the processors are synchronized to obtain optimum performance.

# 1.7.7 Embedded Processor/Embedded Microcontroller

An embedded processor is a processor with special features that allow it to embed multiple processes into the system.

Real time image processing and aerodynamics are two areas where fast, precise and intensive calculations and fast context switching (from one program to another) are essential. Embedded processor is the term sometimes used for processor that has been a specially designed such that it has the following capabilities:

- 1. Fast context switching and thus lower latencies of the tasks in complex real time applications. [Section 4.6] Fast context switching means that the calling program or interrupted service routine CPU registers save and retrieve fast [Section 4.6].

- 2. 32-bit or 64-bit atomic addition and multiplication, and no shared data problem in the operations with large operands with each operand placed in two or four registers. [Section 7.8.1]

- 3. 32-bit RISC core for fast, more precise and intensive calculations by the embedded software.

Embedded microcontroller is the term sometimes used for specially designed microcontrollers that have the following capabilities:

- 1. When a microcontroller has internal RAM, large flash or ROM, timer, interrupt handler, devices and peripherals and there is no external memory or device or peripheral required for the given application.

- 2. Fast context switching and thus lower latencies of the tasks in complex real time applications. For example, ARM and 68HC1x microcontrollers save all CPU registers fast

An embedded processor is term used for processors with fast processing, fast context-switching and atomic ALU operations. An embedded microcontroller is the term used for a microcontroller that has internal RAM, large flash or ROM, timer, interrupt handler, internal devices and internal peripherals and there is no external memory or device or peripheral required for the given application.

**Complex System Embedded Processors** Table 1.7 gives different processors that can embed in a complex system.

Table 1.7 Processors in complex embedded systems

| Processor                                                           | Application Advantage                                                                                                                                                                            |                                                                                                 | Disadvantage                                                                                                       |  |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|

| General Purpose<br>Microprocessor                                   | When intensive computations are required, caches are used and pipeline and superscalar operations are needed and large embedded software is to be located in the external memory cores or chips. | No engineering cost for designing the processor.                                                | Additional redundant execution units that are not needed in the given system design                                |  |

| Mic <b>ro</b> controller                                            | Used with internal memory, devices and peripherals and when embedded software is to be located in the internal ROM or flash.                                                                     | No engineering cost for designing the processor with internal memory, devices and peripherals.  | Additional manufacturing costs and redundant application units which are not needed in the given system design.    |  |

| DS <b>P</b>                                                         | Used with signal processing-related instructions for filters, image, audio, and video and CODEC operations.                                                                                      | No engineering cost involved for designing the signal processor.                                | Manufacturing cost may be high.                                                                                    |  |

| Single purpose processors and application specific system processor | Control IO and bus operations and peripherals and devices.                                                                                                                                       | They support other processing units in the system and execute specific hardware processes fast. | In-house engineering cost of development, royalty payments for an IP core of processor and time-to-market cost.    |  |

| Duál core processor                                                 | To significantly enhance the performance of the system.                                                                                                                                          | Reduced engineering cost.                                                                       | Manufacturing cost, as dual core processors are costly.                                                            |  |

| Accelerator                                                         | To accelerate the execution of codes. A floating point coprocessor accelerates mathematical operations and Java accelerator accelerates Java code execution.                                     | Increases performance by co-processing with the main processor.                                 | Engineering cost of<br>development or royalty<br>payments for IP core of<br>processor and time-to-<br>market cost. |  |

A DSP for mobile phones, for example, OMAP of Texas Instruments, uses the effective power dissipation methods of dynamic switching both for power supply voltage and operating frequency of the CPU core.

For a number of applications, the DSPs cores may not suffice. Domain specific ASIPs have specific instruction sets. For IOs, network, media or security applications, smart card, video game, palm top computer, cell-phone, mobile-Internet, hand-held embedded systems, Gbps transceivers, Gbps LAN systems, satellite or missile systems, we need special processing units in a VLSI circuit designed to function as a processor with an instruction-set for programmability. These special units are called domain-specific ASIP.

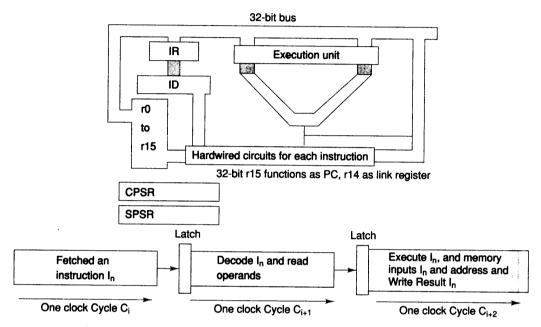

### 1.7.8 Embedding ARM processor

Examples of Stream 4 GPPs in Table 1.4 are ARM 7 and ARM 9. The core of these processors can be embedded onto a VLSI chip or an SoC. An ARM-processor VLSI-architecture is available either as a CPU chip or for integrating it into VLSI or SoC. ARM, Intel and Texas Instruments and several other companies have developed such processors. ARM provides CISC functionality with RISC architecture at the core. The cores of ARM7, ARM9 and their DSP enhancements are available for embedding in systems. [Refer to http:/www.ti.com/sc/ docs/asic/modules/arm7.htm and arm9.htm].

ARM integrates with other features (for example DSP) in new GPPs, which are available from several sources, for example, Intel and Texas Instruments. Exemplary ARM 9 applications are setup boxes, cable modems, and wireless-devices such as mobile handsets.

ARM9 has a single cycle  $16\times32$  multiple accumulate unit. It operates at 200 MHz. It uses  $0.15~\mu m$  GS30 CMOSs. It has a five-stage pipeline. It incorporates RISC core with CISC functions. It integrates with a DSP when designed for an ASIC solution. An example is its integration with DSP is TMS320C55x from Texas Instruments. [Refer to http://www.ti.com/sc/docs/asic/modules/arm7.htm and arm9.htm]

A lower performance but very popular version of ARM9 is ARM7. It operates at 80 MHz. It uses 0.18  $\mu$ m based GS20  $\mu$ m CMOSs. Using ARM7, ARM9 and CORTEX-M3, a large number of embedded systems have recently become available.

Lately, a new class of embedded systems has emerged that additionally incorporates ASSP chips or cores in its design.

#### 1.7.9 Embedding ASSP

Assume that there is an embedded system for real-time video processing. Real-time processing arises for digital television, high definition TV decoders, set-up boxes, DVD (Digital Video Disc) players, web phones, video-conferencing and other systems. An ASSP that is dedicated to these specific tasks alone provides a faster solution. The ASSP is configured and interfaced with the rest of the embedded system.

Assume that there is an embedded system that using a specific protocol interconnects, its units through specific bus architecture to another system. Also, assume that suitable encryption and decryption is required. [The output bit stream encryption protects messages or design from passing to an unknown external entity.] For these tasks, besides embedding the software, it may also be necessary to embed some RTOS features [Section 1.4.6]. If the software alone is used for the above tasks, it may take a longer time than a hardwired solution for application-specific processing. An ASSP chip provides such a solution. For example, an ASSP chip [from i2Chip (http://www.i2Chip.com)] has a TCP, UDP, IP, ARP and Ethernet 10/100 MAC (Media Access Control) hardwired logic included into it. The chip from i2Chip, W3100A, is a unique hardwired Internet connectivity solution. Much needed TCP/IP stack processing software for networking tasks is thus available as a hardwired solution. This gives output five times faster than a software solution using the system's GPP. It is also an RTOS-less solution. Using the same microcontroller in the embedded system to which this ASSP chip

interfaces, Ethernet connectivity can be added. Another ASSP, which is now available, is the 'Serial-to-Ethernet Converter (IIM7100). It does real-time data processing by a hardware protocol stack. It needs no change in the application software or firmware and provides the most economical and smallest RTOS-solution.

An ASSP is used as an additional processing unit for running application specific tasks in place of processing using embedded software.

# **-** 1.8

#### **DESIGN PROCESS IN EMBEDDED SYSTEM**

The concepts used during a design process are as follows.

- 1. <u>Abstraction:</u> Each problem component is first abstracted. For example, in the design of a robotic system, the problem of abstraction can be in terms of control of arms and motors.

- 2. Hardware and Software architecture: Architectures should be well understood before a design.

- 3. <u>Extra functional Properties:</u> Extra functionalities required in the system being developed should be well understood from the design.

- 4. <u>System Related Family of designs:</u> Families of related systems developed earlier should be taken into consideration during designing.

- 5. <u>Modular Design:</u> Modular design concepts should be used. System designing is fast by decomposition of software into modules that are to be implemented. Modules should be such that they can be composed (coupled or integrated) later. Effective modular design should ensure effective (i) function independence, (ii) cohesion and (iii) coupling.

- (a) Modules should be clearly understood and should maintain continuity.

- (b) Also, appropriate protection strategies are necessary for each module. A module is not permitted to change or modify another module functionality. For example, protection from a device driver modifying the configuration of another device.

- 6. <u>Mapping</u>: Mapping into various representations is done from software requirements. For example, data flow in the same path during the program flow can be mapped together as a single entity. Transform and transaction mapping design processes are used in designing. For example, an image is input data to a system; it can have a different number of pixels and colours. The system does not process each pixel and colour individually. Transform mapping of image is done by appropriate compression and storage algorithms. Transaction mapping is done to define the sequence of images.

- 7. <u>User Interface Design:</u> User interface design is an important part of design. User interfaces are designed as per user requirements, analysis of the environment and system functions. For example, in an automatic chocolate vending machine (ACVM) system, the user interface is an LCD multiline graphics display. It can display a welcome message as well as specify the coins needed to be inserted into the machine for each type of chocolate. The same ACVM may be designed with touchscreen User Interface (GUI), or it may be designed with Voice User Interfaces (VUIs). Any of these interface designs has to be validated by the customer. For example, the ACVM customer who installs the machine must validate message language and messages to be displayed before an interface design can proceed to the implementation stage.

- 8. <u>Refinements:</u> Each component and module design needs to be refined iteratively till it becomes the most appropriate for implementation by the software team.

The software design process may require use of Architecture Description Language (ADL). It is used for representing the following: (i) Control Hierarchy (ii) Structural Partitioning (iii) Data Structure and Hierarchy (iv) Software Procedures.

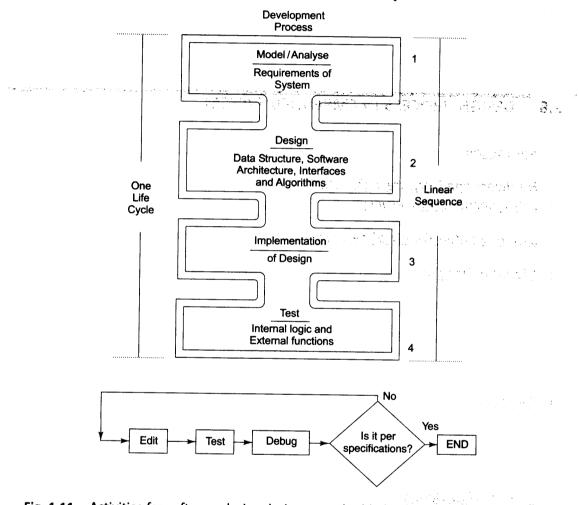

Figure 1.11 shows the activities for software-design cycle during an embedded software-development process and the cycle may be repeated till tests show the verification of specifications.

Fig. 1.11 Activities for software design during an embedded software-development process

# 1.8.1 Design Metrics

A design process takes into account design metrics. There are several design metrics for an embedded system, and these are listed in Table 1.8.

# 1.8.2 Abstraction of Steps in the Design Process

A design process is called bottom-to-top design if it builds by starting from the components. A design process is called top-to-down design if it first starts with abstraction of the process and then after abstraction the details are created. Top-to-down design approach is the most favoured approach. The following lists the five levels of abstraction from top to bottom in the design process:

(1) **Requirements:** Definition and analysis of system requirement. It is only by a complete clarity of the required *purpose*, *inputs*, *outputs*, *functioning*, *design metrics* (Table 1.8) and *validation requirements* for finally developed systems specifications that a well designed system can be created. There has to be consistency in the requirements.

Table 1.8

Design metrics used in the embedded systems

| Design Metrics         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Dissipation      | For many systems, particularly battery operated systems, such as mobile phone or digital camera the power consumed by the system is an important feature. The battery needs to be recharged less frequently if power dissipation is small.                                                                                                                                                                                                                                             |

| Performance            | Instructions execution time in the system measures the performance. Smaller execution time means higher performance. For example, a mobile phone, voice signals processed between antenna and speaker in 0.1s shows phone performance. Consider another. For example, a digital camera, shooting a 4M pixel still image in 0.5s shows the camera performance.                                                                                                                          |

| Process deadlines      | There are number of processes in the system, for example, keypad input processing, graphic display refresh, audio signals processing and video signals processing. These have deadlines within which each of them may be required to finish computations and give results.                                                                                                                                                                                                             |

| User interfaces        | These include keypad GUIs and VUIs.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Size                   | Size of the system is measured in terms of (i) physical space required, (ii) RAM in kB and internal flash memory requirements in MB or GB for running the software and for data storage and (iii) number of million logic gates in the hardware.                                                                                                                                                                                                                                       |

| Engineering cost       | Initial cost of developing, debugging and testing the hardware and software is called engineering cost and is a one-time non-recurring cost.                                                                                                                                                                                                                                                                                                                                           |

| Manufacturing cost     | Cost of manufacturing each unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Flexibility            | Flexibility in design enables, without any significant engineering cost, development of different versions of a product and advanced versions later on. For example, software enhancement by adding extra functions necessitated by changing environment and software re-engineering.                                                                                                                                                                                                  |

| Prototype              | Time taken in days or months for developing the prototype and in-house testing for system                                                                                                                                                                                                                                                                                                                                                                                              |

| development time       | functionalities. It includes engineering time and making the prototype time.                                                                                                                                                                                                                                                                                                                                                                                                           |

| Time-to-market         | Time taken in days or months after prototype development to put a product for users and consumers.                                                                                                                                                                                                                                                                                                                                                                                     |

| System and user safety | System safety in terms of accidental fall from hand or table, theft (e.g., a phone locking ability and tracing ability) and in terms of user safety when using a product (for example, automobile brake or engine).                                                                                                                                                                                                                                                                    |

| Maintenance            | Maintenance means changeability and additions to the system; for example, adding or updating software, data and hardware. Example of software maintenance is additional service or functionality software. Example of data maintenance is additional ring-tones, wallpapers, video-clips in mobile phone or extending card expiry date in case of smart card. Example of hardware maintenance is additional memory or changing the memory stick in mobile computer and digital camera. |

- (2) **Specifications:** Clear specifications of the required system are must. Specifications need to be precise. Specifications guide customer expectations from the product. They also guide system architecture. The designer needs specifications for (i) hardware, for example, peripherals, devices processor and memory specifications, (ii) data types and processing specifications, (iii) expected system behaviour specifications, (iv) constraints of design, and (v) expected life cycle specifications. Process specifications are analysed by making lists of inputs on events, outputs on events and how the processes activate on each event (interrupt).

- (3) **Architecture:** Data modeling designs of attributes of data structure, data flow graphs (Section 6.2), program models (Section 6.1), software architecture layers and hardware architecture are defined. Software architectural layers are as follows:

- 1. The first layer is an architectural design. Here, a design for system architecture is developed. The question arises as to how the different elements—data structures, databases, algorithms, control functions, state transition functions, process, data and program flow—are to be organised.

- 2. The second layer consists of data-design. Questions at this stage are as follows. What design of data structures and databases would be most appropriate for the given problem? Whether data organised as a tree- like structure will be appropriate? What will be the design of the components in the data? [For example, video information will have two components, image and sound.]

- 3. The third layer consists of interface design. Important questions at this stage are as follows. What shall be the interfaces to integrate the components? What is the design for system integration? What shall be design of interfaces used for taking inputs from the data objects, structures and databases and for delivering outputs? What will be the port structure for receiving inputs and transmitting outputs?

- (4) Components: The fourth layer is a component level design. The question at this stage is as follows. What shall be the design of each component? There is an additional requirement in the design of embedded systems, that each component should be optimised for memory usage and power dissipation. Components of hardware, processes, interfaces and algorithms. The following lists the common hardware components:

- 1. Processor, ASIP and single purpose processors in the system

- 2. Memory RAM, ROM or internal and external flash or secondary memory in the system

- 3. Peripherals and devices internal and external to the system

- 4. Ports and buses in the system

- 5. Power source or battery in the system

During software development process we can model the components as object-oriented. Table 1.9 lists the stages as components-based object-oriented software development process.

(5) **System Integration:** Built components are integrated in the system. Components may work fine independently, but when integrated may not fullfil the design metrics. The system is made to function and validated. Appropriate tests are chosen. Debugging tools are used to correct erroneous functioning.

Each component and its interface system is integrated after the design stage. Program implementation is in a language and may use an integrated development environment (IDE), and source code engineering tools, which should follow the model, software architecture and design specifications. Program simplicity should be maintained during the implementation process.

The design stages range from abstraction to detailed designing to verification activities. Continuous refinement in design can be made by effective communication between designers and implementers. Software design can be assumed to consist of four layers: architecture design, data design, interfaces design and component level design.

Table 1.9 Components-based object-oriented software development process

| Effo <b>rt</b> | Activities                                                                                                  | Model Deficiency                                   |

|----------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Stage 1        | Components that could be used in software development identified                                            |                                                    |

| Stage 2        | Selection of available classes (single logically bonded groups) from a software components resource library | Need for robust interfaces and slow development in |

| Stage 3        | Sort components, which are available and reusable by re-engineering and which are unavailable               | case the reusable components are not               |

| Stage 4        | Re-engineer components and create unavailable components                                                    | available in required                              |

| Stage 5        | Construct software from the components and test them                                                        | numbers                                            |

| Stage 6        | Iteratively construct till final validation of software                                                     |                                                    |

**Actions at each step** Research by software engineering experts have shown that on an average, a designer needs to spend about 50% of the time for planning, analysis and design, 40% for testing, validation and debugging and 10–15% on coding. Action required to be taken at each step in the design process is listed in Table 1.10.

Table 1.10 Action to be taken at each step of design process

| Description                                                                                  |  |  |

|----------------------------------------------------------------------------------------------|--|--|

| Design is analyzed                                                                           |  |  |

| The result of analysis is used to improve design to meet specifications and metrics          |  |  |

| System design must be verified to ensure that it meets the design metrics given in Table 1.8 |  |  |

|                                                                                              |  |  |

# 1.8.3 Challenges in Embedded System Design: Optimizing Design Metrics

Following are the challenges that arise during the design process.

Amount and type of hardware needed: Optimizing the requirement of microprocessors, ASIPs and single purpose processors in the system on the basis of performance, power dissipation, cost and other design metrics are the challenges in a system design. A designer also chooses the appropriate hardware (memory RAM, ROM or internal and external flash or secondary memory, peripherals and devices internal and external ports and buses and power source or battery) taking into account the design metrics given in Table 1.8; for example, power dissipation, physical size, number of gates and the engineering, prototype development and manufacturing costs.

**Optimizing Power Dissipation and Consumption:** Power, consumption during the operational and idle state of system should be optimal. The following methods are used to meet the design challenges.

Clock Rate Reduction Power dissipation typically reduces 2.5  $\mu$ W per 100 kHz of reduced clock rate. So reduction from 8000 kHz to 100 kHz reduces power dissipation by about 200  $\mu$ W, which is nearly similar to when the clock is nonfunctional. [Remember, total power dissipated (energy required) may not reduce. This is because on reducing the clock rate, the computations will take a longer time and total energy required equals the power dissipation per second multiplied by computation time].

The power  $25 \,\mu\text{W}$  is typically the residual dissipation needed to operate the timers and few other units. By operating the clock at a lower frequency or during the power-down mode of the processor, the advantages are as follows: (i) Power loss due to heat generation reduces. (ii) Radio frequency interference also reduces due to the reduced power dissipation within the gates. [Radiated RF (Radio Frequency) power depends on the RF current inside a gate, which reduces due to increase in 'ON' state resistance between drain and channel of each MOSFET transistor and that reduces heat generation.]

**Voltage Reduction** In portable or hand-held devices such as a cellular phone, compared to 5 V operation, a CMOS circuit power dissipation reduces by one sixth,  $\sim (2V/5V)^2$ , in 2.0 V operation. Thus the time intervals needed for recharging the battery increase by a factor of six.

Wait, Stop and Cache Disable Instructions An embedded system may need to be run continuously, without being switched off; the system design, therefore, is constrained by the need to limit power dissipation while it is ON but is in idle state. Total power consumption by the system while in running, waiting and idle states should be limited. A microcontroller must provide for executing Wait and Stop instructions for the power-down mode. One way to reduce power dissipation is to cleverly incorporate into software the Wait and Stop instructions. Another is to operate the system at the lowest voltage levels in the idle state and selecting power-down mode in that state. Yet another method is to disable use of certain structural units of the processor—for example, caches—when not necessary and to keep in disconnected state those structure units that are not needed during a particular software execution, for example timers or IO units.

Operations can be performed at low voltage or reduced clock rate in order to control power dissipation. For embedded system software, performance analysis during its design phase must also include the analysis of power dissipation during program execution and during standby. An embedded system has to perform tasks continuously from power-up to power-off and may even be kept 'ON' continuously. Clever real-time programming by using 'Wait' and 'Stop' instructions and disabling certain units when not needed is one method of saving power during program execution.

**Process Deadlines** Meeting the deadline of all processes in the system while keeping the memory, power dissipation, processor clock rate and cost at minimum is a challenge.

Flexibility and Upgrade ability Flexibility and upgrade ability in design while keeping the cost minimum and without any significant engineering cost is a challenge. Flexibility and upgrade ability allow different and advanced versions of a product to be introduced in the market later on.

**Reliability** Designing a reliable product by appropriate design, testing and thorough verification, is a challenge. The goal of testing is to find errors and to validate that the implemented software is as per the specifications and requirements. Verification refers to an activity to ensure that specific functions are correctly implemented. Validation refers to an activity to ensure that the system that has been created is as per the requirements agreed upon at the analysis phase, and to ensure its quality.

# 1.9 FORMALIZATION OF SYSTEM DESIGN

Formalization of system design is done using a top-down approach by abstraction (Section 1.8.2) and by

Detailing requirements and specifications of hardware and software

- Defining architectures of hardware and software

- Coding and implementation as per architecture

- Testing, validation and verification of system

Since a diagrammatic model clears the design concepts better than abstraction, a modeling language, for formalization can be used. The Universal Modeling Language (UML) is used. In UML, a designer describes the following:

- 1. 'User Diagram', 'Object Diagram', 'Sequence Diagram', 'State Diagram', 'Class Diagram' and 'Activity Diagram'

- 2. Classes and Objects, which describe identity, attributes, components and behaviour

- 3. Inheritances of the classes and objects

- 4. Interfaces of the objects and their implementation at the objects

- 5. Structural description of the design components

- 6. Behavioral description in terms of states, state machine and signals (Section 6.3)

- 7. Events description

Section 6.5 will describe UML in detail. Chapters 11 and 12 will describe the model design examples in detail.

# 1.10 DESIGN PROCESS AND DESIGN EXAMPLES

#### 1.10.1 System Design Process Examples

Chapters 11 and 12 will describe design examples in detail.

#### 1.10.2 Automatic Chocolate Vending Machine (ACVM)

Let us consider an automatic chocolate vending machine. This interesting example given here helps a reader to understand several concepts of programming an embedded system as a multitasking system.

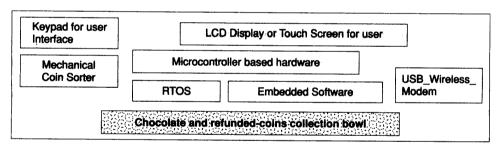

Figure 1.12 shows the diagrammatic representation of ACVM. Assume that ACVM has following components:

- 1. It has keypad on the top of the machine. That enables a child to interact with it when buying a chocolate. The owner can also command and interact with the machine.

- 2. It has an LCD display unit on the top of the machine. It displays menus, text entered into the ACVM and pictograms, welcome, thank you and other messages. It enables the child as well as the ACVM owner to graphically interact with the machine. It also displays time and date. (For GUIs, the keypad and LCD display units or touch screen are basic units.)

- 3. It has a coin insertion slot and a mechanical coin sorter so that child can insert coins to buy a chocolate.

- 4. It has a delivery slot so that child can collect the chocolate and coins, if refunded.

- 5. It has an Internet connection port using a USB based wireless modem so that owner can know status of the ACVM sales from a remote location.

#### **ACVM Functions** Assume that ACVM functions are as follows:

- 1. The ACVM displays the GUIs and if the child wishes to enter contact information, birthday information or get answer to FAQs, it displays the appropriate menu.

- 2. It displays a welcome message when in idle state. It also continuously displays time and date at the right bottom corner of display screen. It can also intermittently display news, weather data or advertisements or important information of interest during idle state.

- 3. When first coin is inserted, a timer also starts. The child is expected to insert all required coins in 2 minutes.

- 4. After 2 minutes the ACVM will display a query to the child if the child does not insert sufficient coins. If the query is not answered the coins are refunded.

- 5. Within 2 minutes if sufficient coins are collected, it displays the message, 'Thanks, wait for few moments please!', delivers the chocolate through the delivery slot and displays message, 'Collect the chocolate and visit again, please!'

### Hardware units ACVM embeds the following hardware units.

- 1. Microcontroller or ASIP (Application Specific Instruction Set Processor)

- 2. RAM for storing temporary variables and stack

- 3. ROM for application codes and RTOS codes for scheduling the tasks

- 4. Flash memory for storing user preferences, contact data, user address, user date of birth, user identification code, answers of FAQs

- 5. Timer and interrupt controller

- 6. A TCP/IP port (Internet broadband connection) to the ACVM for remote control and for the owner to get ACVM status reports

- 7. ACVM specific hardware to sort coins of different denominations. Each denomination coin generates a set of status and input bits and port-interrupts. Using an ISR for that port, the ACVM processor reads the port status and input bits. The bits give the information about which coin has been inserted. After each read operation, the status bits are reset by the routine

- 8. Power supply

Fig. 1.12 Diagrammatic representation of the ACVM

#### **Software components** ACVM embeds the following software components:

- 1. Keypad input read task

- 2. Display task

- 3. Read coins task for finding coins sorted

- 4. Deliver chocolate task

- 5. TCP/IP stack processing task

- 6. TCP/IP stack communication task

#### 1.10.3 Smart Card

Smart card is one of the most used embedded system today. It is used for credit-debit bankcard, ATM card, e-purse or e-Wallet card, identification card, medical card (for history and diagnosis details) and card for a

number of new innovative applications. [Reader may refer to a frequently updated website, http://www.sguthery@tiac.net for the answers of frequently asked questions about cards.] The security aspect is of paramount importance for smart card use, when used for financial and banking-related transactions. [Reader may refer to http://www.home.hkstar.com/~alanchan/papers/smartCardSecurity/ and http://www.research.ibm.com/secure\_systems/scard.htm for details of the card-security requirements.]

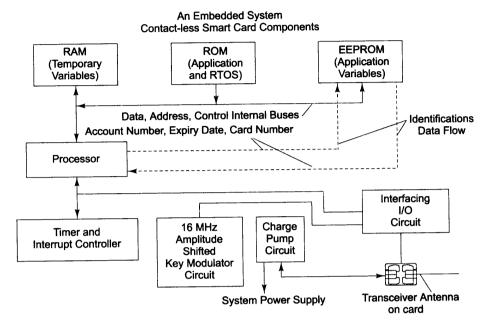

The smart card is a plastic card ISO standard dimensions,  $85.60 \times 53.98 \times 0.80$  mm. It is an embedded system on a card: SoC (System-On-Chip). ISO recommended standards are ISO7816 (1 to 4) for host-machine contact-based cards and ISO14443 (Part A or B) for the contactless cards. The silicon chip is just a few multimeters in size and is concealed in-between the layers. Its very small size protects the card from bending. Figure 1.13 shows embedded-system hardware components for a contactless smart card.

Fig. 1.13 Embedded hardware components in a contact less smart card

**Embedded Hardware** The embedded hardware components are as follows:

- Microcontroller or ASIP

- · RAM for temporary variables and stack

- One time programmable ROM for application codes and RTOS codes for scheduling the tasks

- Flash for storing user data, user address, user identification codes, card number and expiry date

- Timer and interrupt controller

- A carrier frequency ~16 MHz generating circuit and Amplitude Shifted Key (ASK) modulator

- Interfacing circuit for the IOs

- Charge pump for delivering power to the antenna for transmission and for system circuits. The charge pump stores charge from received RF (radio frequency) at the card antenna in its vicinity. [The charge pump is a simple circuit that consists of the diode and high value ferroelectrics material-based capacitor.]

The details of the basic hardware units are as follows:

- 1. The Microcontroller used can be MC68HC11D0 or PIC16C84 or a smart card processor Philips Smart XA or a similar ASIP Processor. MC68HC11D0 has 8 kB internal RAM and 32 kB EPROM and 2/3 wire protected memory. Most cards use 8-bit CPUs. The recent introduction in the cards is of a 32-bit RISC CPU. A smart card CPU should have special features, for example, a security lock. The lock is for a certain sections of the memory. A protection bit at the microcontroller may protect 1 kB or more data from modification and access by any external source or instructions outside that memory. Once the protection bit is placed at the maskable ROM in the microcontroller, the instructions or data within that part of the memory are accessible from instructions in that part only (internally) and not accessible from the external instructions or instructions outside that part. The CPU may disable access by blocking the write cycle placement of the data bits on the buses for instructions and data protection at the physical memory after certain phases of card initialization and before issuing the card to the user. Another way of protecting is as follows: The CPU may access by using the physical addresses, which are different from the logical address used in the program.

- 2. ROM is used in the card. The usual size is 8 or 64 kB for usual or advanced cryptographic features in the card, respectively. Full or part of ROM bus activates only after a security check. The processor protects a part of the memory from access. The ROM stores the following.

- i. Fabrication key, which is a unique secret key for each card. It is inserted during fabrication.

- ii. Personalization key, which is inserted after the chip is tested on a printed circuit board. Physical addresses are used in the testing phase. The key preserves the fabrication key and this key insertion preserves the card personalization. After insertion of this key, RTOS and applications use only logical addresses.

- iii. RTOS codes

- iv. Application codes

- v. A utilization lock to prevent modification of two PINs and to prevent access to the OS and application instructions. It stores after the card enters the utilization phase.

- 3. **EEPROM or Flash** is scalable. These means that only that part of the memory required for a particular operation will unlock for use. The authorizer will use the required part; the application will use the other part. It is protected by the access conditions stored therein. It stores the following:

- i. PIN (Personal Identification Number), the allotment and writing of which is by the authorizer (for example, a bank) and its use is possible by the latter only by using the personalization and fabrication keys. It is for identifying the card user in future transactions. Card user is given this key. Alternatively, a modifiable password is given to the user and password opens the PIN key.

- ii. An unblocking PIN for use by the authorizer (say the bank). Through this key, the card circuit identifies the authorizer before unblocking. Data of the user unblocks for the authorizer and storing of information on the card is possible by the authorizer through the host.

- iii. Access conditions for various hierarchically arranged data files.

- iv. Card user data, for example, name, bank and branch identification number and account number or health insurance details.

- v. Data post issue that the application generates. For example, in case of e-purse, the details of previous transactions and current balance. Medical history and diagnosis details and/or previous insurance claims and pending insurance claims record in case of a medical card.

- vi. It also stores the application's non-volatile data.

- vii. Invalidation lock sent by the host after the expiry period or card misuse and user account closing request. It locks the data files of the master or elementary individual file or both.

- 4. **RAM** stores the temporary variables and stack during card operations by running the OS and the *application*.

- 5. Chip power supply voltage extracts by a charge pump circuit. The pump extracts the charge from the signals from the host analogous to what a mouse does in a computer and delivers the regulated voltage to the card chip, memory and IO system. Signals can be from antenna or from clock pin. In a typical card operation using 0.18 μm technology, 1.6 to 5.5 V is the threshold limit and for a 0.35 μm technology, 2.7 to 5.5 V.

- 6. **IO System** of chip and host interact through asynchronous serial UART (Section 3.2.3) at 9.6 k or 106 k or 115.2 k baud/s. The chip interconnects to a card hosting system (reader and writer) either through the gold contacts or through a centimeter sized antenna on each side. The latter provides *contactless* interconnection between the IO pins, which are meant for *contact-based* interaction, RST (Reset Signal from host) and Clock (from host).

- 7. Wireless Communication for IO interaction is by radiations through the antenna coils for contactless interaction. The card and host interact through a card modem and a host modem. The application protocol data unit (APDU) is a standard for communication between the card and host computer. Modulation is with 10% index amplitude modulating carrier of 13.66–13.56 Mbps ASK (amplitude shifted keying) is used for contactless communication at data rates of ~1 Mbps. One-sixteenth frequency subcarrier modulates through BPSK (Binary Phase Shifted Keying).

# **Embedded Software** Smart card embeds the following software components:

- 1. Boot-up, initialisation and OS programs

- 2. Smart card secure file system

- 3. Connection establishment and termination

- 4. Communication with host

- 5. Cryptography algorithm

- 6. Host authentication

- 7. Card authentication

- 8. Saving addition parameters or recent new data sent by the host (for example, present balance left)